# Low Power Decoding Circuits for Ultra Portable Devices

Reza Meraji

Doctoral Dissertation Circuits and Systems Lund, October 2014

Reza Meraji Department of Electrical and Information Technology Circuits and Systems Lund University P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral dissertations ISSN 1654-790X; No. 64 ISBN 978-91-7623-057-2 (pdf)

© 2014 Reza Meraji Typeset in Palatino and Helvetica using LATEX 2<sub>E</sub>. Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this dissertation may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

## Popular Science Summary

Over the years, considerable advances have been made in wireless communication. Driven by the mobile phone industry, most of the previous efforts have been concentrated on improving data rates, to provide a wide range of services to the users. However, plenty of applications exist and more are emerging that can benefit from low rate and short range wireless communication devices. Such devices can be used in any portable electronics product with applications in the field of healthcare, sports and fitness, wearable gadgets, PC peripherals, industrial monitoring and automation, gaming devices, and plenty of other consumer electronics. More specifically, due to the aging population of the world and increased attention to health awareness in recent years, the healthcare and fitness industry have a huge application potential.

General purpose, short range wireless standards such as Bluetooth or Zig-Bee have been around for some time. Such standards have made life of users more comfortable by providing a wide range of services such as facilitating wireless connection to smart phones, tablets, TVs and other electronic devices. However, that has been achieved at the cost of increased power consumption, resulting in an inconvenience obligation for regular battery recharging or replacement. In these standards, circuit modules dedicated to handle radio connectivity, drain considerable amount of energy from the battery. Consequently, one design aspect that has become very important in recent years is reducing the power consumption. Specifically, with increasing miniaturization of devices, power has become a top priority design consideration that has motivated researchers to find techniques for reducing power consumption in all components of system during the design period.

Battery technology is not improving in coherence with the increased demands of the processing power. Furthermore, in many applications there is an upper limit to the physical size of the battery and thus on the total amount of energy available. There are many cases, such as in medical implantable electronics or *install and forget* remote sensor networks, where the battery is desired to last the life-time of the device, as recharging or battery replacement is either difficult or not feasible. What can be achieved with the available power budget depends on how efficiently, in terms of energy, the corresponding integrated circuits for radio connectivity operate.

Another relevant circuit design aspect is the physical dimension. A smaller integrated circuit is always desired as it requires less resources and will reduces the cost in mass production. Furthermore, it will be easier for a smaller circuit to fit in a miniature product. All these eventually will result in a more affordable product for the potential users.

An important hardware component that can help to reduce the total power consumption in a wireless communication link is the *error control* circuitry. Error control, or *error detection and correction*, are referred to techniques that facilitate reliable delivery of digital data over poor conditions of a communication channel. In many cases, error control techniques enable reconstruction of the original transmitted data from the corrupted received data due to passing through an unreliable channel. Also, for similar quality of service, error control components aid to reduce the transmission power and hence save more energy. To benefit the most from error control circuits and reduce the total power consumption of the device, it is critical to design such circuits to operate as power efficiently as possible.

In this dissertation, in the framework of a low rate, short range and low power wireless system, low power implementation methods for error control circuits are investigated. Channel decoding circuits that are implemented according to either low power digital or analog circuit design techniques are fundamentally different. Each of these approaches introduces different sets of design challenges. Accordingly, simulations and low power design techniques are followed. Furthermore, attempts to deal with various challenges in the design period are presented. Consequently, alternative low power circuit architectures both in analog and digital domains are proposed, fabricated at an industrial facility and evaluated through laboratory measurements. The proposed decoder integrated circuits are analyzed in terms of critical aspects such as coding gain, required silicon area, speed of operation, energy effi-

ciency and minimum power needed for successful operation.

The research work presented in this dissertation is fulfilled as part of the project *Wireless Communication for Ultra Portable Devices*. The project is funded by a grant from the Swedish Foundation for Strategic Research (*Stiftelsen för Strategisk Forskning - SSF*). The chip fabrications have been carried out by STMicroelectronics.

to my mother and in memory of my father

### **Abstract**

A wide spread of existing and emerging battery driven wireless devices do not necessarily demand high data rates. Rather, ultra low power, portability and low cost are the most desired characteristics. Examples of such applications are wireless sensor networks (WSN), body area networks (BAN), and a variety of medical implants and health-care aids. Being small, cheap and low power for the individual transceiver nodes, let those to be used in abundance in remote places, where access for maintenance or recharging the battery is limited. In such scenarios, the lifetime of the battery, in most cases, determines the lifetime of the individual nodes. Therefore, energy consumption has to be so low that the nodes remain operational for an extended period of time, even up to a few years. It is known that using error correcting codes (ECC) in a wireless link can potentially help to reduce the transmit power considerably. However, the power consumption of the coding-decoding hardware itself is critical in an ultra low power transceiver node. Power and silicon area overhead of coding-decoding circuitry needs to be kept at a minimum in the total energy and cost budget of the transceiver node. In this thesis, low power approaches in decoding circuits in the framework of the mentioned applications and use cases are investigated. The presented work is based on the 65 nm CMOS technology and is structured in four parts as follows:

In the first part, goals and objectives, background theory and fundamentals of the presented work is introduced. Also, the ECC block in coordination with its surrounding environment, a low power receiver chain, is presented. Designing and implementing an ultra low power and low cost wireless transceiver node introduces challenges that requires special considerations at various levels of abstraction. Similarly, a competitive solution often occurs after a conclusive design space exploration. The proposed decoder cir-

cuits in the following parts are designed to be embedded in the low power receiver chain, that is introduced in the first part.

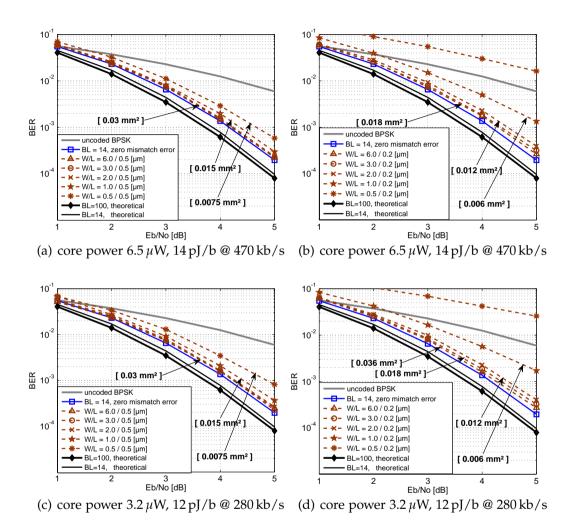

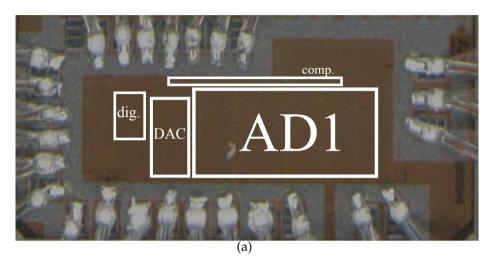

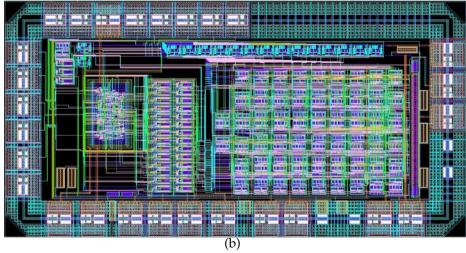

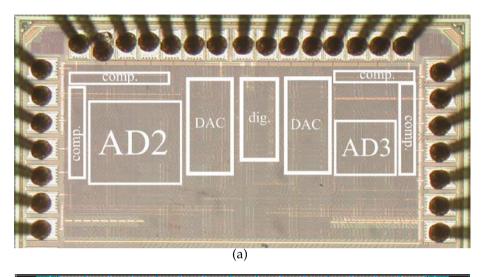

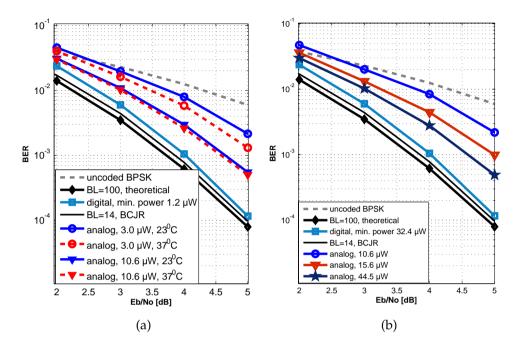

Second part, explores analog decoding method and its capabilities to be embedded in a compact and low power transceiver node. Analog decoding method has been theoretically introduced over a decade ago that followed with early proof of concept circuits that promised it to be a feasible low power solution. Still, with the increased popularity of low power sensor networks, it has not been clear how an analog decoding approach performs in terms of power, silicon area, data rate and integrity of calculations in recent technologies and for low data rates. Ultra low power budget, small size requirement and more relaxed demands on data rates suggests a decoding circuit with limited complexity. Therefore, the four-state (7,5) codes are considered for hardware implementation. Simulations to chose the critical design factors are presented. Consequently, to evaluate critical specifications of the decoding circuit, three versions of analog decoding circuit with different transistor dimensions fabricated. The measurements results reveal different trade-off possibilities as well as the potentials and limitations of the analog decoding approach for the target applications. Measurements seem to be crucial, since the available computer-aided design (CAD) tools provide limited assistance and precision, given the amount of calculations and parameters that has to be included in the simulations. The largest analog decoding core (AD1) takes 0.104 mm<sup>2</sup> on silicon and the other two (AD2 and AD3) take 0.035 mm<sup>2</sup> and 0.015 mm<sup>2</sup>, respectively. Consequently, coding gain in trade-off with silicon area and throughput is presented. The analog decoders operate with 0.8 V supply. The achieved coding gain is 2.3 dB at bit error rates (BER)=0.001 and 10 pico-Joules per bit (pJ/b) energy efficiency is reached at 2 Mbps.

Third part of this thesis, proposes an alternative low power digital decoding approach for the same codes. The desired compact and low power goal has been pursued by designing an equivalent digital decoding circuit that is fabricated in 65 nm CMOS technology and operates in low voltage (nearthreshold) region. The architecture of the design is optimized in system and circuit levels to propose a competitive digital alternative. Similarly, critical specifications of the decoder in terms of power, area, data rate (speed) and integrity are reported according to the measurements. The digital implementation with 0.11 mm<sup>2</sup> area, consumes minimum energy at 0.32 V supply which gives 9 pJ/b energy efficiency at 125 kb/s and 2.9 dB coding gain at BER=0.001.

The forth and last part, compares the proposed design alternatives based on the fabricated chips and the results attained from the measurements to conclude the most suitable solution for the considered target applications. Advantages and disadvantages of both approaches are discussed. Possible extensions of this work is introduced as future work.

### **Preface**

#### **Journal Articles**

• R. Meraji, Y. Sherazi, J. B. Anderson, H. Sjöland, V. Öwall, »A Comparison of Low Power Analog and Digital (7,5) Convolutional Decoders in 65 nm CMOS,« submitted to IEEE Transactions on Circuits and Systems I: Regular papers (TCAS I).

**contribution:** This article concludes the research work on low power decoder and shows trade-offs among critical specifications of the sub-threshold digital and analog decoders. The effect of transistor dimensions on the performance of the analog decoding circuit is investigated through measurements. The paper concludes with the implementation approach (digital or analog) that is most suitable for the targetted compact and ultra low power, low rate radio receiver. The entire work has been carried out by the first author, with some assistance from the second author in digital implementation, and under supervision of the remaining authors.

• H. SJÖLAND, J. B. ANDERSON, C. BRYANT, R. CHANDRA, O. EDFORS, A. JOHANSSON, N. SEYED MAZLOUM, R. MERAJI, P. NILSSON, D. RADJEN, J. RODRIGUES, Y. SHERAZI, V. ÖWALL, »A receiver architecture for devices in wireless body area networks, « *IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS)*, vol., no., Month 2012.

**contribution:** The research work has been performed jointly with the other authors, under supervision of the first author. This article partly included in the thesis, mainly the part that is the contribution from the author of this thesis. This part includes the simulated performance of the low power decoder, in the proposed ultra low power radio receiver through system simulations.

### **Peer Reviewed Conference Papers**

In the following papers, the major research work has been performed by the first author, with contributions from the remaining authors.

H. SJÖLAND, J. B. ANDERSON, C. BRYANT, R. CHANDRA, O. EDFORS, A. JOHANSSON, N. SEYED MAZLOUM, R. MERAJI, P. NILSSON, D. RADJEN, J. RODRIGUES, Y. SHERAZI, V. ÖWALL, »Ultra low power transceivers for wireless sensors and body area networks,« 8th International Symposium on Medical Information and Communication Technology (ISMICT), Firenze, Italy, apr. 2014.

**contribution:** The research work has been performed jointly with the other authors, under supervision of the first author.

R. Meraji, Y. Sherazi, J. B. Anderson, H. Sjöland, V. Öwall, »Analog and Digital Approaches for an Energy Efficient Low Complexity Channel Decoder,« international symposium on circuits and systems (ISCAS), Beijing, may 2013.

**contribution:** This paper is based on simulations and synthesis results that presents a study of analog and digital versions of a low complexity channel decoder to investigate the overall performance of both circuits in 65 nm CMOS for moderate bit rate applications.

• R. Meraji, J. B. Anderson, H. Sjöland, V. Öwall, »A 3 uW 500 kb/s Ultra Low Power Analog Decoder with Digital I/O in 65 nm CMOS, « *International Conference on Electronics and Communication Systems (ICECS)*, Abu Dhabi, dec 2013.

**contribution:** This paper presents the measurement results on the analog decoing chip with digital interface in 65nm CMOS.

• R. Meraji, J. B. Anderson, H. Sjöland, V. Öwall, »An Analog (7,5) Convolutional Decoder in 65 nm CMOS for Low Power Wireless Applications, « international symposium on circuits and systems (ISCAS), Rio de Janeiro, may 2011.

**contribution:** Mainly, the architecture of an analog decoder for emdedding in a conventional digital receiver is presented. Simulations on the performance, expected power consumption at simulated throughput are carried out.

• R. Meraji, J. B. Anderson, H. Sjöland, V. Öwall, »Transistor sizing for a 4-state current mode analog channel decoder in 65-nm CMOS, « NORCHIP, Lund, Sweden, nov 2011.

**contribution:** A simulation technique combining Monte-Carlo analysis in Spectre with Matlab processing has been used to investigate suitable transistor sizing for an analog (7,5) convolutional decoder.

• R. Meraji, J. B. Anderson, H. Sjöland, V. Öwall, »A low power analog channel decoder for ultra portable devices in 65 nm technology, « *NORCHIP*, Tampere, Finland, nov 2010.

**contribution:** This work investigates an analog Hamming decoder with peripheral data converter and digital interface circuitry performance in 65nm CMOS. The architecture of the decoding core is mainly based on previously published works in older technologies.

The research work included in this dissertation is supported by the Swedish Foundation for Strategic Research. Chip fabrications are supported by STMicroelectronics.

# Acknowledgments

Apart from the efforts of myself, the finalization of this dissertation was not possible without the support of many others. I take this opportunity to express my appreciation to the people who have been encouraging me in pursuing my doctoral degree.

First and foremost, I would like to express my sincere gratitude to my main supervisor Professor Viktor Öwall. I cannot thank him enough for his tremendous support and help. He has not only well guided me to my academic achievements, but also has inspired me to experience more, read better, try new things and broaden my horizons. I could not have imagined having a better supervisor for my PhD study.

I would like to extend my special appreciation to my co-supervisor Professor John B. Anderson for giving me valuable advices and for all the enjoyable discussions that we had.

I would like to thank Professor Henrik Sjöland for his excellent management of the UPD project, which I was part of. I am indebted to him for his so many useful technical comments and feedback, that helped me to improve my work. I am also thankful to Dr. Carl Bryant, Dr. Yasser Sherazi, Dr. Dejan Radjen, Nafiseh Seyed Mazloum and Dr. Rohit Chandra for being great project teammates.

Being part of the Digital ASIC group has been a wonderful experience for me. Apart from all that I have learned from our numerous technical and nontechnical discussions, it has left me unforgettable pleasant memories from all the fun times that we had together during workshops, group activities, conference trips, after-works and barbecue evenings. For all these, I am truly grateful to my former and present colleagues and friends: Dr. Deepak Dasalakunte, Dr. Johan Löfgren, Dr. Isael Diaz, Dr. Yasser Sherazi, Dr. Chenxin Zhang, Dr. Liang Liu, Associate Professor Joachim Rodriguez, Rakesh Gangarajaiah, Hemanth Prabhu, Oskar Andersson, Babak Mohammadi, Michal Stala, Yangxurui Liu and Professor Peter Nilsson. Indeed, I have had the most enjoyable time working with a group of amazing more recent colleagues in the Digital ASIC group: Steffen Malkowsky, Christoph Müller, Farrokh Ghani Zadegan, Dimitar Nikolov, Breeta SenGupta and Professor Erik Larsson.

Special thanks to Pia Bruhn, Doris Glöck, Anne Andersson, Erik Jonsson, Robert Johnsson, Bertil Lindvall, Stefan Molund, Martin Nilsson, Lars Hedenstjerna, and Josef Wajnblom for taking care of all technical and administrative issues.

There are more friends and colleagues that deserve my appreciation. The list will be long, so I thank you all and wish you all the bests!

Finally, I would like to show my deepest gratitude to my mother for her patience and unconditional support. And my father, though I lost him more than ten years ago, he is still inspiring me to reach ever further.

Lund, October 2014

Reza Merenjo

# Contents

| Pr | eface |                                            | xiii |

|----|-------|--------------------------------------------|------|

| A  | cknov | wledgments                                 | xvi  |

| Co | onten | ts                                         | xix  |

| 1  | Intr  | oduction                                   | 3    |

|    | 1.1   | Motivation                                 | 3    |

|    | 1.2   | Error Control Methods in Wireless Networks | 4    |

|    | 1.3   | Energy Considerations in a coded System    | 4    |

|    | 1.4   | Target Applications                        | 6    |

|    | 1.5   | Background Survey                          | 7    |

|    | 1.6   | Challenges                                 | 10   |

|    | 1.7   | Research Objectives and Contributions      | 10   |

|    | 1.8   | Outline of the thesis                      | 12   |

| 2  | Ultı  | ra Low Power Radio                         | 15   |

|    | 2.1   | Introduction                               | 15   |

|    | 2.2   | The Vision                                 | 16   |

|    | 2.3   | The UPD system overview                    | 17   |

|    | 2.4   | UPD Modulation Scheme                      | 20   |

|   | 2.5  | Low power radio standards                                   | 23 |

|---|------|-------------------------------------------------------------|----|

|   | 2.6  | Relevance and challenges of sub-threshold design            | 23 |

| 3 | Fun  | damentals of MOSFET Sub-threshold Operation                 | 25 |

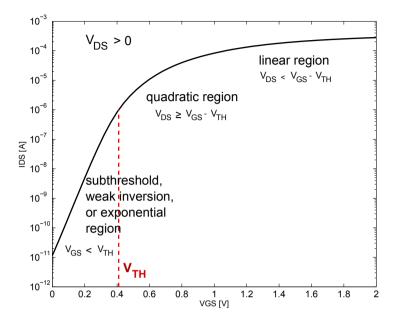

|   | 3.1  | MOS Transistor Basic Regions of Operation                   | 25 |

|   | 3.2  | MOS Transistor Regions of Operation at Low Drain Currents   | 26 |

|   | 3.3  | MOS model in weak inversion region                          | 28 |

|   | 3.4  | Sub-threshold MOS Ultra Low Power Circuits                  | 29 |

|   | 3.5  | Circuit Design Considerations in Sub-threshold              | 29 |

| 4 | Sele | ection of the Coding Scheme                                 | 33 |

|   | 4.1  | Benefits of error control codes                             | 33 |

|   | 4.2  | System and hardware considerations for a coded transmission | 34 |

|   | 4.3  | Coding Scheme                                               | 35 |

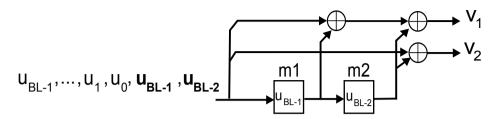

|   | 4.4  | Soft Decision Decoding                                      | 36 |

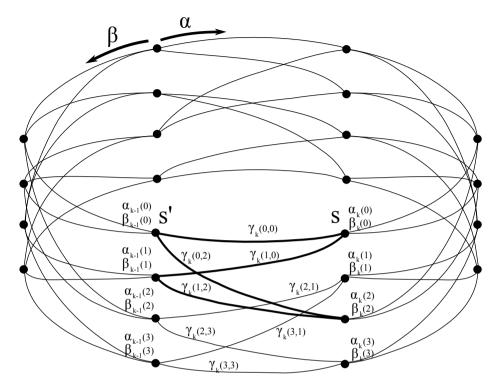

|   | 4.5  | Trellis Representation of Convolutional Codes               | 36 |

|   | 4.6  | Tail-biting codes                                           | 36 |

|   | 4.7  | The Generic Sum-Product Decoding Algorithm                  | 37 |

|   | 4.8  | The BCJR Decoding Algorithm                                 | 38 |

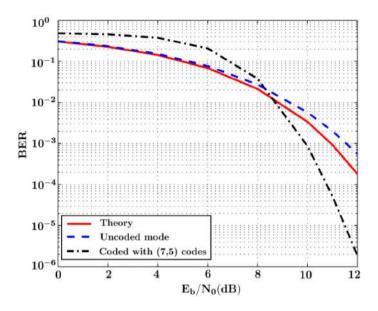

|   | 4.9  | System Level UPD Baseband simulation                        | 40 |

| 5 | Low  | Power Analog Decoding                                       | 43 |

|   | 5.1  | Decoding in Analog                                          | 43 |

|   | 5.2  | Analog Decoding Basic Calculations: A Simplified Model      | 44 |

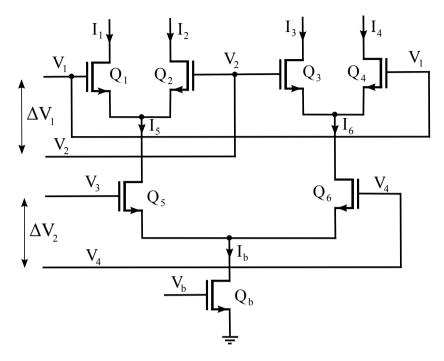

|   | 5.3  | Forward-Backward Computations                               | 50 |

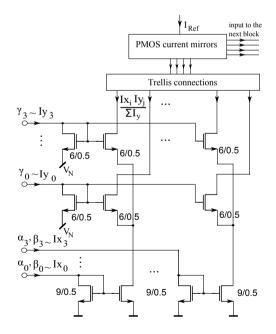

|   | 5.4  | Operation of an Analog Decoding Core                        | 52 |

| 6 | Har  | dware Mapping of the Analog Decoding Circuit                | 55 |

|   | 6.1  | System Perspective                                          | 55 |

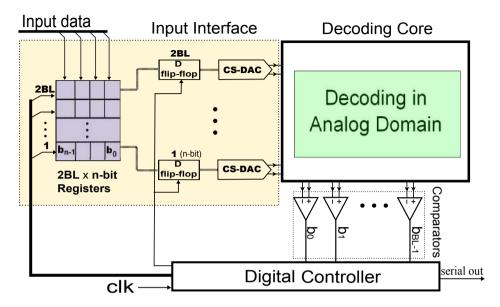

|   | 6.2  | Top-Level Architecture of the Decoder                       | 56 |

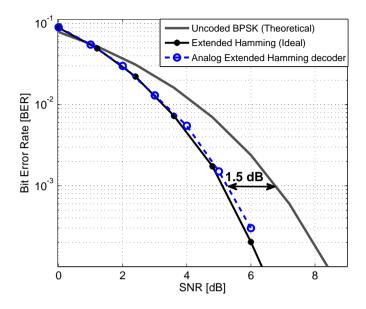

|   | 6.3  | Extended (8,4) Hamming Decoder: A Brief Investigation       | 58 |

|   | 6.4  | (7,5) Analog Decoding Circuit                               | 63 |

|    | 6.5   | Circuit Details                             | 68  |

|----|-------|---------------------------------------------|-----|

|    | 6.6   | Fabricated Analog Decoders                  | 69  |

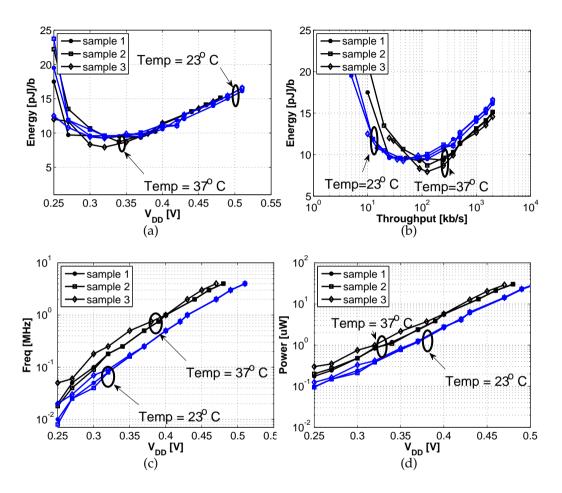

| 7  | Perf  | ormance of Analog Decoding Circuits         | 77  |

|    | 7.1   | Objectives                                  | 77  |

|    | 7.2   | Measurement Setup                           | 78  |

|    | 7.3   | Analog Decoder Mesurements                  | 79  |

|    | 7.4   | Observations from the Measurements          | 83  |

| 8  | Low   | Power Digital Design Techniques             | 91  |

|    | 8.1   | Power consumption in a digital CMOS circuit | 91  |

|    | 8.2   | Dynamic power reduction                     | 92  |

|    | 8.3   | Short circuit power reduction               | 95  |

|    | 8.4   | Leakage power reduction                     | 95  |

| 9  | Desi  | igning of the Digital Decoding Circuit      | 99  |

|    | 9.1   | Basics of Low Power Digital Decoder         | 99  |

|    | 9.2   | The max-log MAP BER performance             | 100 |

|    | 9.3   | Architecture                                | 101 |

|    | 9.4   | Synthesis at nominal voltage                | 103 |

| 10 | Perf  | ormance of Digital Decoding Circuit         | 107 |

|    | 10.1  | Objectives                                  | 107 |

|    | 10.2  | Measurement Setup                           | 107 |

|    | 10.3  | Reduced Voltage Measurement Results         | 108 |

| 11 | Ana   | log versus Digital: Analysis of the Results | 113 |

|    | 11.1  | Analog and Digital: an analysis             | 113 |

| 12 | Sum   | ımary                                       | 117 |

| Re | feren | ices                                        | 119 |

# **List of Figures**

| 1.1 | Sample UPD target applications                                           | 6    |

|-----|--------------------------------------------------------------------------|------|

| 2.1 | UPD receiver architecture                                                | 17   |

| 2.2 | UPD modulation. The direction of rotation on the I/Q dia-                |      |

|     | gram determines the transmitted coded symbol for each in-                |      |

|     | formation bit.                                                           | _ 22 |

| 2.3 | The ideal BFSK modulation spectrum used in UPD with $\pm 250\mathrm{kF}$ |      |

|     | in-band transmission, corresponding to 250 kb/s                          | 22   |

| 3.1 | Operation regions for an NMOS transistor                                 | 27   |

| 4.1 | Structure of encoder and memory initialization for the (7,5)             |      |

|     | tail-biting convolutional codes                                          | 37   |

| 4.2 | Tail-biting trellis structure for the 4-state (7,5) convolutional        |      |

|     | codes with block length (BL) = $6$                                       | 38   |

| 4.3 | UPD BER in thermal noise                                                 | 40   |

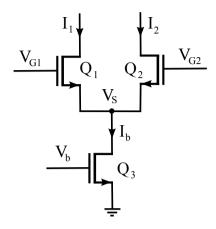

| 5.1 | Stack of NMOS transistors                                                | 45   |

| 5.2 | A pair of diode connected PMOS transistors                               | 47   |

| 5.3 | Gilbert vector multiplier with differential inputs                       | 48   |

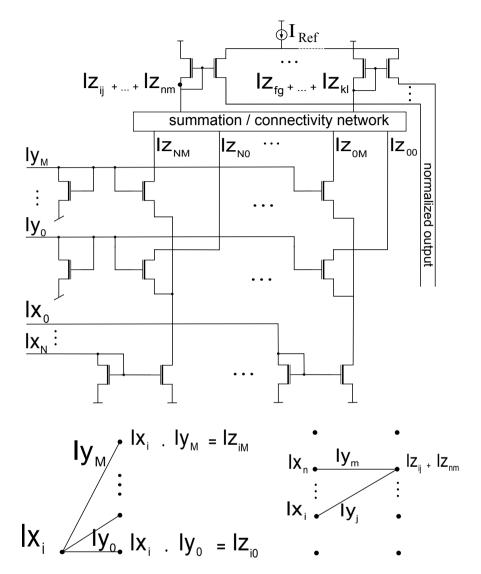

| 5.4 | Generalized Gilbert multiplier network for implementing the              |      |

|     | sum-product algorithm shown with corresponding trellis rep-              |      |

|     | resentation                                                              | 51   |

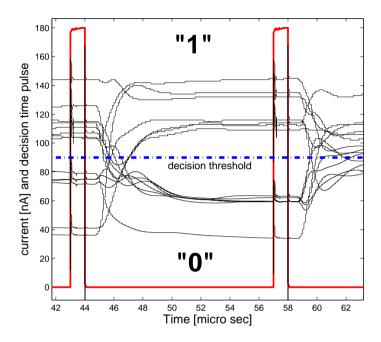

| 5.5 | Transient plots of the decoded output bits in an analog de-              |      |

|     | coder represented by low level currents                                  | 52   |

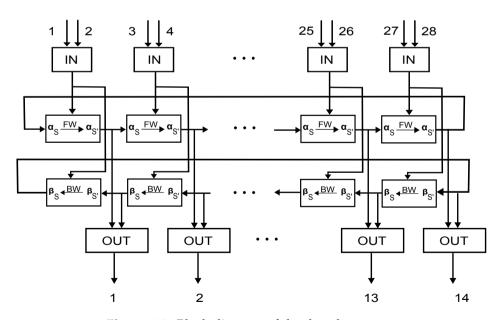

| 6.1 | Architecture of the analog decoding circuit                              | 58   |

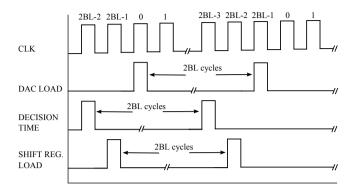

| 6.2 | Timing diagram of the decoder. 2 BL clock cycles is the dedi-            |      |

|     | cated time for decoding                                                  | 59   |

| 6.3 | Bit error rate performance, 2.5 Mb/s                                     | 61   |

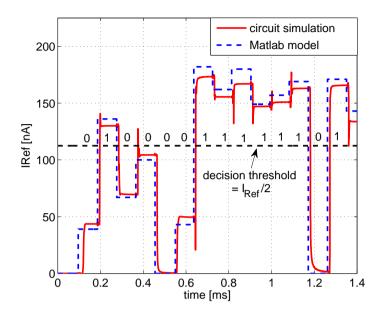

| 6.4        | Sample soft bit output for Matlab model in comparison with circuit simulations.                                                | 64  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

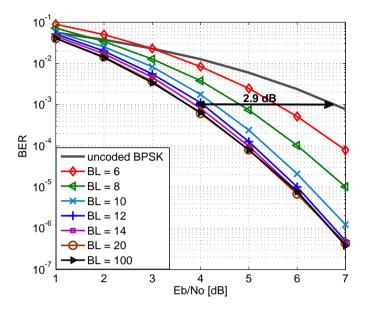

| 6.5        | BER performance of the (7,5) decoder for different BL                                                                          | 65  |

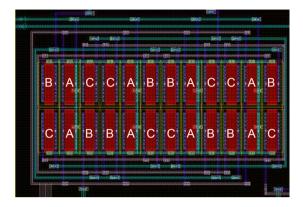

| 6.7        | Sample 2-dimensional matching of transistors used in the in-                                                                   | 00  |

| 0.7        | put cells                                                                                                                      | 72  |

| 6.8        | Block diagram of the decoder core                                                                                              | 72  |

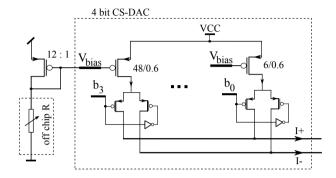

| 6.9        | Current steering DACS with binary weighting                                                                                    | 73  |

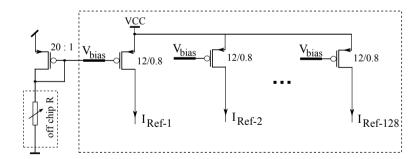

| 6.10       | Implemented current sources                                                                                                    | 73  |

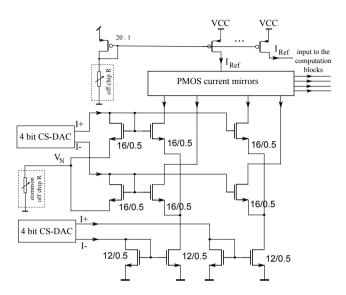

| 6.11       | Input cell                                                                                                                     | 74  |

| 6.12       | Computing blocks                                                                                                               | 74  |

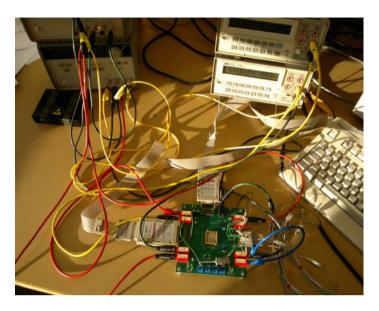

| 7.1<br>7.3 | Measurement setup                                                                                                              | 78  |

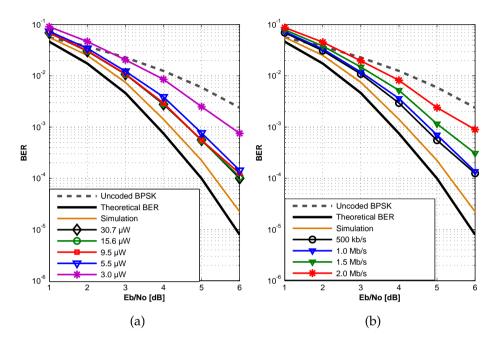

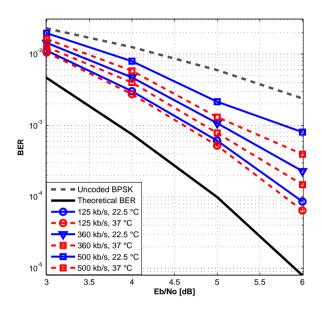

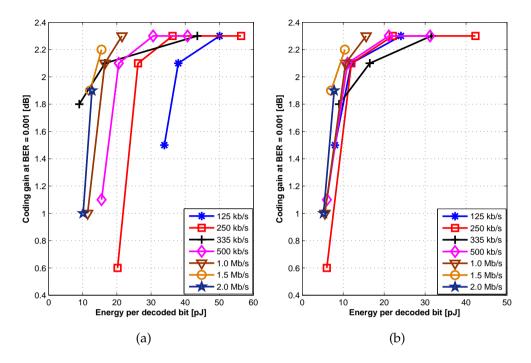

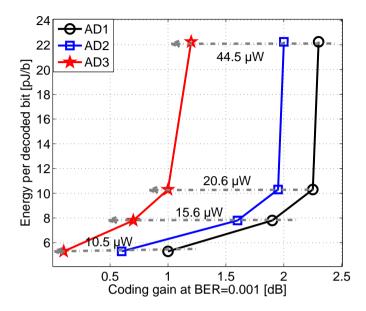

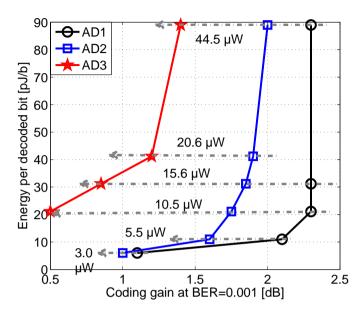

|            | $\mu$ W                                                                                                                        | 81  |

| 7.5        | Measured coding gains for AD1,2,3 at 2 Mb/s                                                                                    | 83  |

| 7.6        | Measured coding gains for AD1,2,3 at 500 kb/s                                                                                  | 84  |

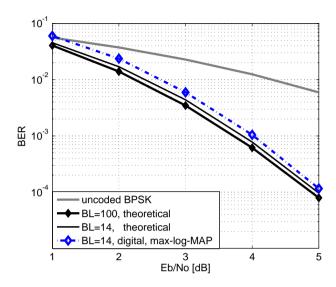

| 9.1        | BER performance of the max-log-MAP algorithm applied on tail-biting (7,5) codes with BL=14                                     | 100 |

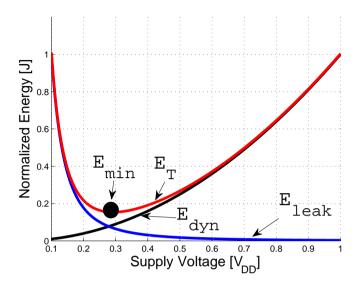

| 9.2        | Typical energy dissipation behavior in a digital circuit for 65 nm CMOS                                                        | 101 |

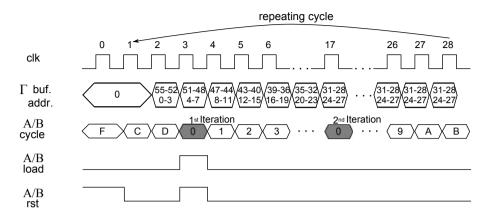

| 9.3        | Timing diagram to perform iterations and recursive calcula-                                                                    |     |

|            | tions of A and B metrics in the digital decoder                                                                                | 103 |

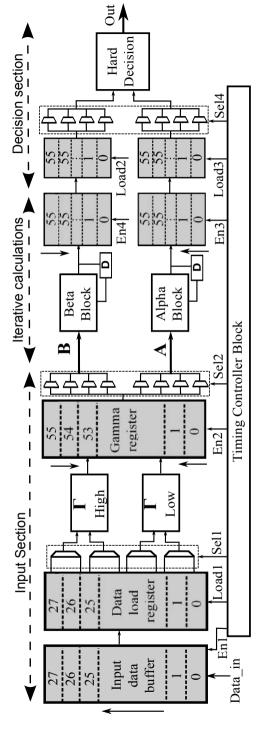

| 9.4        | Complete architecture of the implemented digital max-log-                                                                      |     |

|            | MAP decoder                                                                                                                    | 105 |

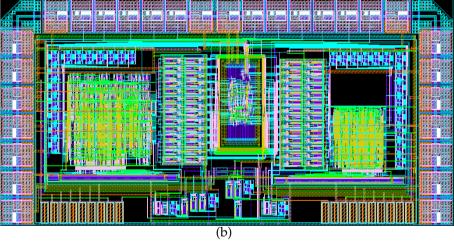

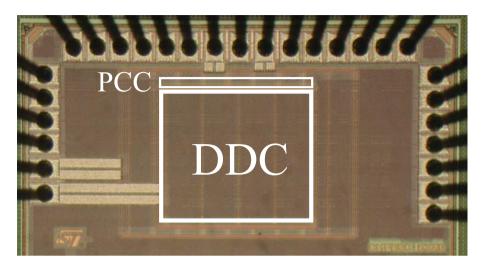

| 9.5        | Die photo of the fabricated digital decoder                                                                                    | 106 |

| 9.6        | Layout of the fabricated digital decoder                                                                                       | 106 |

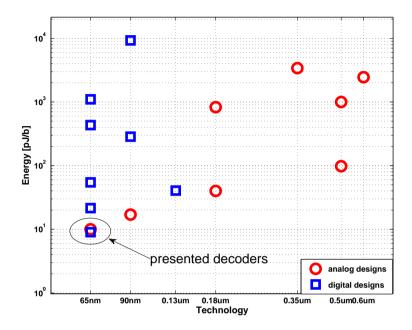

| 11.2       | Measured normalized energy per decoded bit evolution over technology generations for analog: [6] [25] [31] [75] [79] [82] [85] |     |

|            | and digital [19] [38] [44] [60] [69] [88] [92] decoders                                                                        | 116 |

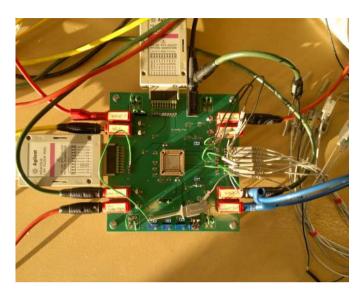

| .1         | PCB and setup for measuring the analog decoding chip, AD1.                                                                     | 132 |

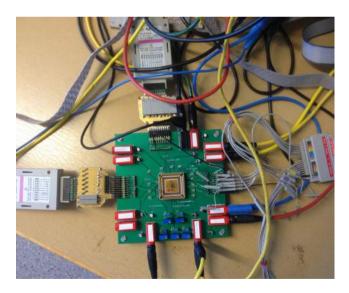

| .2         | PCB and setup for measuring the analog decoding chip, AD2                                                                      |     |

|            | and AD3                                                                                                                        | 132 |

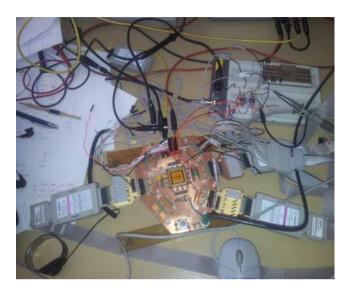

| .3         | PCB and setup for measuring the digital decoding chips                                                                         | 133 |

| .4         | Measurement instruments and the environment chamber                                                                            | 133 |

# **List of Tables**

| 2.1  | UPD project target specifications                            | 16  |

|------|--------------------------------------------------------------|-----|

| 2.2  | UPD initial power budget allocation                          | 21  |

| 6.1  | Power consumption of different sections of the decoder       | 61  |

| 6.2  | Analog decoder characteristics                               | 62  |

| 6.3  | Energy comparison for Analog Hamming decoders                | 62  |

| 6.4  | Transistor dimensions of fabricated analog decoding cores    | 69  |

| 7.1  | Digital interface characteristics                            | 79  |

| 7.2  | AD1's fixed and random errors at 500 kb/s, test experiment 1 | 85  |

| 7.3  | AD1's fixed and random errors at 1.5 Mb/s, test experiment 1 | 85  |

| 7.4  | AD3's fixed and random errors at 500 kb/s, test experiment 1 | 86  |

| 7.5  | AD3's fixed and random errors at 1.5 Mb/s, test experiment 1 | 86  |

| 7.6  | AD1's fixed and random errors at 1.5 Mb/s, test experiment 2 | 87  |

| 7.7  | AD3's fixed and random errors at 500 kb/s, test experiment 2 | 88  |

| 7.8  | AD3's fixed and random errors at 1.5 Mb/s, test experiment 2 | 88  |

| 9.1  | Synthesized digital decoder characteristics                  | 104 |

| 11 1 | Decoder Comparison                                           | 114 |

## Acronyms

ADC Analog-to-Digital Converter. 19, 55

**ADi** Analog Decoding Circuit *i*. 69

**ARQ** Automatic Repeat Request. 4

**AWGN** Additive White Gaussian Noise. 60

**BAN** Body Area Networks. 15

**BER** Bit Error Rate. 3

**BFSK** Binary Frequency Shift Keying. 21

**BL** Block Length. 35

BPSK Binary Phase Shift Keying. 23

**BTLE** Bluetooth Low Energy. 22

**CAD** Computer Aided Design. 9

**CMOS** Complementary Metal-Oxide-Semiconductor. 6

CS-DAC Current Steering Digital-to-Analog Converter. 56

**DAC** Digital-to-Analog Converter. 55

**DDC** Digital Decoding Core. 102

**DFF** D Flip-Flop. 56

**DRAM** Dynamic Random Access Memories. 93

**ECC** Error Control Code. 3

**EMV** Energy Minimum Voltage. 98

**GFSK** Gaussian Frequency Shift Keying. 22

**HVT** High Threshold Voltage. 95

**I and Q** In phase and Quadrature phase. 20

**ISM** Industrial, Scientific and Medical. 15

LDPC Low-Density Parity-Check. 9

**LLR** Log-Likelihood Ratio. 39

**LNA** Low Noise Amplifier. 18

**LO** Local Oscillator. 18

**LP-HVT** Low Power-High Threshold Voltage. 60

**LP-SVT** Low Power Standard Threshold Voltage. 101

**LVT** Low Threshold Voltage. 95

MAC Media Access Control. 19

**MAP** Maximum a Posteriori. 39

MC Monte-Carlo. 64

MOS Metal Oxide Semiconductor. 25

**OOK** On-Off Keying. 21

**OQPSK** Offset Quadrature Phase Shift Keying. 23

**PCC** Peripheral Communication Core. 102

**RF** Radio-Frequency. 17

**SNR** Signal to Noise Ratio. 3, 5

**SP** Sum-Product algorithm. 37

**SRAM** Static Random Access Memories. 93

**SVT** Standard Threshold Voltage. 95

TB Tail-Biting. 36

**TD-AMS** Time-Domain Analog and digital Mixed-Signal processing. 116

**UPD** Ultra Portable Devices. 6

**VHDL** V(ery high speed integrated circuit) Hardware Description Language. 101

WBAN Wireless Body Area Networks. 16

**WSN** Wireless Sensor Networks. 15

### Glossaries

| BL Block length of the codes. 56             |  |  |  |  |  |

|----------------------------------------------|--|--|--|--|--|

| C <sub>L</sub> Load capacitance. 91          |  |  |  |  |  |

| $C_{ox}$ Oxide capacitance per unit area. 26 |  |  |  |  |  |

| $E_b$ Energy per bit. 34                     |  |  |  |  |  |

| $I_{Ref}$ Reference current. 50              |  |  |  |  |  |

| <i>I</i> <sub>S</sub> Specific current. 28   |  |  |  |  |  |

| L Gate length of a transistor. 30            |  |  |  |  |  |

| $N_0$ Noise power spectral density. 34       |  |  |  |  |  |

|                                              |  |  |  |  |  |

$U_T$  Thermal voltage also known as the Boltzmann voltage. 28

$V_{CC}$  Supply voltage in analog domain. 67

$V_{DS}$  Drain to source voltage of a transistor. 26

$V_{GS}$  Gate to source voltage of a transistor. 26

$A_{V_T}$  Technology dependent proportionality constant. 30

$A_{\beta}$  Technology dependent proportionality constant. 30

$V_{SAT}$  Saturation velocity. 31

$V_{SB}$  Source to substrate voltage of a transistor. 31

$V_{TH}$  Threshold voltage. 26

W Gate width of a transistor. 30

$\Delta\Sigma$  Delta-Sigma data converter. 19

$\alpha_{SW}$  Switching activity factor. 91

$\alpha_{V_{SAT}}$  An empirical parameter. 32

$\alpha_{V_{TH}}$  An empirical parameter. 32

$\alpha_u$  An empirical parameter. 32

$\frac{W}{T}$  Width-to-length ratio of a transistor. 28

$\gamma_{SP}$  The scaling factor in the Sum-Product algorithm. 38

$\mu$  Mobility of the electric carrier. 26

f Frequency. 31

$g_m$  Transistor's trans-conductance. 28

$i_{n,d}$  Drain current thermal noise. 31

$k_f$  An empirical coefficient in the gate voltage flicker noise model. 31

n Subthreshold slope factor. 28

$v_{n,f}$  Gate voltage flicker noise. 31

**sub-** $V_{\rm T}$  Sub-threshold. 7

# Part I

### Introduction

#### 1.1. MOTIVATION

The presence of wireless links in our daily life is constantly increasing. Many new exciting applications, in addition to increased attentions to health care practices, have stimulated interests on battery-supplied, ultra low power wireless devices. Such devices can be worn, placed in locations where access is difficult or implanted in the human body. Therefore, these devices need to be small, inexpensive and have a reasonably long battery lifetime, i.e. operate on an extremely limited power budget. Such demands introduce great challenges throughout the design process. While high data rates are not needed in most scenarios, maintaining communication reliability under ultra low power operation is critical.

In order to minimize the errors that occur during transmission over a lossy channel, Error Control Code (ECC)s can be enforced. In a coded transmission, ECCs are used in communication systems to either improve the overall Signal to Noise Ratio (SNR) in the system, or help to reduce the transmission power for a similar Bit Error Rate (BER) performance with respect to an uncoded transmission.

With ever increasing popularity of the mentioned low power wireless devices, small scale decoding circuits are likely to attract more attention, especially when power consumption and silicon area are among the critical design factors. It is worth to note that due to the relatively massive amount of computations required in the decoding algorithms, decoding circuits are particularly power demanding and are major sinks of energy in a receiver

4 Introduction

chain. Therefore, using ECCs and energy efficient implementation of the corresponding decoding circuits can greatly prolong the battery lifetime of the wireless transceiver nodes.

#### 1.2. ERROR CONTROL METHODS IN WIRELESS NETWORKS

The common practiced methodology for error control in wireless links or networks are divided into two main approaches.

One method is referred to as the Automatic Repeat Request (ARQ). When the receiver detects an error in the transmitted data packet, it automatically requests the transmitter for re-transmission. This process is repeated until the packet is either received error-free or the number of repetitions exceeds a predetermined number. However, this method is inefficient in bad channel conditions, especially when we deal with energy and latency.

The second method is using an ECC scheme. ECCs are used in various communication systems to provide more reliable transmission of data by fixing some of the errors that occur during transmission through a lossy channel. ECCs require more processing power at transceiver nodes, mainly to execute the corresponding decoding algorithms. Error correction capability of ECCs is directly related to complexity of the generated codes. Powerful codes are likely to increase the processing energy consumption at the receiver in decoding process. Sine the powerful codes have higher decoding complexity; therefore, demand higher energy for decoding process. In this work, rather small scale channel decoders have been chosen; firstly to fit the target application in the section 1.4, and secondly to be able to fulfill all the research objectives as described in the section 1.7.

#### 1.3. ENERGY CONSIDERATIONS IN A CODED SYSTEM

Although, employing ECCs could be beneficial in a communication system to reduce power consumption or to improve the quality of data transmission, one should also consider the underlying trade-offs in the design process. The decoding algorithms in general are computationally complex and when implemented in hardware require a noticeable amount of power to decode the message.

In a coded communication system the decoder fixes some of the errors that occurs over the channel. Therefore, when the bit error rate requirements are

kept the same, the transmit power can be reduced with respect to the uncoded system since the system can operate at lower SNRs for the same BERs. That helps to save the power, and hence increase the battery lifetime of the transceiver. The price of this reduction in power, is the hardware overhead of the encoder and decoder as well as the power consumption of theses blocks. In fact, the complexity and power are much more significant in the decoder hardware than the encoder. For a conventional long range communication link, the transmit power is normally much higher in comparison with the power consumption of the receiver chain. However, for short range transmission links, the transmit power is also reduced with respect to the distance between the transmit and receive nodes. In these scenarios, the total energy dissipation is no more dominated by the radio transmission energy alone. Instead radio energy together with the computation energy in the transmitting and receiving nodes could take comparable shares in the total energy requirements of a communication link [30].

Encoding a message adds redundancy to the data. That makes the coded data which are often called *codewords*, or simply *codes* to contain more bits than the message itself. Codes must be powerful enough to not only compensate for the corresponding reduced SNR levels at the receiver, but also result in reduced number of errors after demodulation and decoding processes.

Circuits that implement a decoding algorithm perform substantial computations, and therefore, are one of the power hungry block in a receiver chain. At the same time, for a certain BER requirement, the amount of energy that is saved by reduction in transmit power in a coded transmission must then be reasonably greater than the energy dissipated during the encoding-decoding process. Also, because of added redundancies in a coded transmission, extra processing is needed in other components of the system to deal with the increased data rates. Consequently, if the codes are not chosen suitably or the decoder hardware is not designed properly, there is a possibility that the total power consumption in the system will not be less than that in an uncoded system. In other words, the power consumption of the decoder circuitry dominates the saving in the transmit power. Using an ECC block might not be efficient if the power saved in transmission is instead dissipated as power consumption of the ECC circuit itself [71].

Another matter to note is the complexity of the codes. Stronger codes provide better BER performance with less transmit power requirements, but with respect to simpler codes, demand decoders with higher complexity. Hence,

6 Introduction

Figure 1.1.: Sample UPD target applications.

more power budget is required. With respect to the target application, a tradeoff typically considered between error correction capability of the codes and decoder complexity.

#### 1.4. TARGET APPLICATIONS

Wireless standardization is a costly and time-consuming process. In order to deploy the available resources in an efficient way, complex, general purpose and massively produced radio transmitters and receivers are generally expected to conform to industry standards. If we consider a bottom-up strategy, a suitable candidate sub-block in a wireless system might not necessarily be one that offers significant reduction in power consumption, but instead would be the one that fits well into the system without demanding drastic changes in the currently agreed and well developed standard. Despite this, there exist plenty of present and emerging applications that allow for a fully custom design in a quest to provide a superior performance rather than a

more affordable design cost. Consequently, following the target application requirements, decoding circuits can be implemented in many different methods and their corresponding algorithms.

The main target of this work is proposing a low power decoding circuits for *Ultra Portable Devices (UPD)*; i.e. custom, small scale, short range and low power radio devices that may include wireless sensor nodes, near body communications, medical implants or modern hearing aid devices. Such applications do not usually demand very high data rates. In most cases the range of required throughput is from a few kb/s up to only a few Mb/s. As a matter of fact, the overall physical dimension and power consumption are the critical aspects. Small physical dimension is critical for implanted devices; therefore, it is desired to reduce implementation costs as well as better portability in on or near body communications. Low power operation is crucial to prolong the battery-driven life-time of the device specially in cases where access is difficult such as medical implants, or as for remotely placed sensor nodes.

#### 1.5. BACKGROUND SURVEY

To find a suitable solution for extremely small and power constrained applications, two different low power approaches in  $65\,\mathrm{nm}$  Complementary Metal-Oxide-Semiconductor (CMOS) technology are investigated; one approach is based on weak inversion operating current mode analog decoding, and the other approach is digital decoding in the sub- $V_{\mathrm{T}}$  region.

#### 1.5.1. ANALOG DECODING

Analog decoding was initially proposed by Hagenauer [33] [32] and Loeliger [45] [47]. The idea then further developed by other researches to emphasis on its efficiencies and benefits in various applications, [1], [87], [57], [7],, [73]. In this method, simple blocks of analog circuitry are used as basic processing units. These blocks are then arranged in a complex fully connected network, whose architecture and connections are determined by the corresponding trellis or graph of the selected codes. It has been observed that analog computation is much faster and less power consuming than digital. In certain applications, analog computations may achieve the robustness of digital systems but consume several orders of magnitude less power. Similarly, the motivation to use analog circuits for decoding has been based on faster analog continu-

8 Introduction

ous time processing compared to digital designs, while consuming less power from the supply. Considerably fewer number of transistors also promised area efficient analog decoding circuits.

The idea has been pursued by other researchers to demonstrate the advantage of implementing the soft iterative decoding algorithms in analog circuitry over digital implementations in terms of silicon area, speed and power consumption [46], [51], [22]. Initially, simple analog decoders were realized in hardware using bipolar transistors. Since CMOS devices biased in the weak inversion, referred to as the sub-threshold (sub- $V_T$ ) region, show similar I-V exponential behavior as bipolar transistors, in recent years they have been used to successfully implement iterative decoding algorithms in analog circuitry. As an example, an analog Hamming decoder correctly operating in sub- $V_T$  region was fabricated in 0.18 $\mu$ m CMOS and the measurement results are reported in [53] and [82]. Early analog decoders claimed to provide significant improvements in consumed power from several times to even more than two orders of magnitude compared to their digital counterparts [46] [51].

Likewise, over the last decade, several analog decoding chips have been fabricated and the results have been presented in the literature [75], [25], [79], [82], [85], [31]. In most cases, the published works reflected merely proof of concept circuits. An attempt in [79] to employ analog decoding concept in a realistic error correcting turbo code for mobile phone standards, was not followed in later technologies. One major drawback of designing analog decoders for complex applications such as high speed cellular phone data transfer is that due to fully parallel computing, the silicon area requirement grows proportionally with respect to the complexity of the codes. Since, mismatch, process and threshold voltage variations affect the overall bit error rate, performances of analog decoders tend to degrade with scaling technologies. These effects impose a lower bound on the physical size of the decoder. While digital designs benefit the most from shrinking in the technology, scaling is usually not welcomed in analog designs. Being no exception, analog decoders suffer from increased mismatch and other imperfection errors. As shown in [91], the number of errors are more significant when the complexity of the decoder is increased; however, small scale decoders were discussed to be more resilient to mismatch errors.

As mentioned earlier, for high speed applications, early power and area advantages of analog decoders over digital designs have deteriorated. In addition, as shown in [91], complex analog decoding circuits are prone to severe

1.6. Challenges

BER performance degradation. The errors due to transistor mismatches may completely ruin the error correction property of the implemented decoding algorithm. Such unresolved issues in the past few years, subsided the initial enthusiastic interests on designing of complex analog decoding circuits for high speed applications.

#### 1.5.2. DIGITAL DECODING

For decoders implemented in the digital domain, technology scaling has constantly improved both area and power consumption. Analog decoders initially found to be smaller and much more power efficient than their digital equivalents. However, as mentioned earlier, constant technology shrinking trend in the most recent years has moderated those gaps between the two approaches towards power efficient design of the decoding circuits.

Furthermore, low voltage operation in todays technologies offers significant savings in power consumption. In [86] the scaling trend on the energy efficiency of analog and digital decoders has been investigated based on the published works over the last decade. There, also an efficient Gallager-style [24], digital Low-Density Parity-Check (LDPC) decoder is presented for sub- $V_T$  operation and is evaluated via simulations based on the models described in [66] and [5]. It is shown that the power consumption is reduced considerably for sub- $V_T$  digital implementations, compared to standard super-threshold (super- $V_T$ ) implementation. For digital designs, however, while the dynamic power quadratically decreases with voltage scaling, the leakage power does not scale as dynamic power, which suggests a minimum energy point. Moreover, speed of processing becomes significantly slower in sub- $V_T$  operating digital circuits.

Digital decoders, benefit from the technology scaling and can achieve increased power efficiency at high throughput. However, limited complexity analog decoders may still remain desirable in terms of area and energy at low to moderate throughput [91]. When digital designs are operated at lower speeds, the dynamic power consumption is reduced, while the static leakage power remains. This results in a degradation of the digital decoders' energy efficiency for low throughput applications.

10 Introduction

#### 1.6. CHALLENGES

Pursuing low power and hardware efficient analog and low voltage digital decoding approaches introduces various challenges. One particular issue is the limited assistance that is provided by the Computer Aided Design (CAD) tools compared to their service in conventional industry standard design flows. Due to the numerous transistors that are needed in an analog decoding circuit, in addition to to the nature of testing and verifying decoding circuits for functional validity, transient-time simulations become extremely time consuming. This places a huge obstacle for repeated simulations that are usually needed for optimizing the design. Furthermore, the lack of a reliable methodology to verify trustworthiness of analog decoder designs before sign-off for fabrication is a major inconvenience.

Likewise, for the digital designs intended to operate on lower voltages than the nominal voltage in a particular technology there exists several restraints. For one thing, deriving accurate and reliable estimates for power consumption and speed of processing in near-threshold voltage operation is problematic. This is because standard cell library models provided by vendors are not normally calibrated for extreme low voltage operation levels. One other challenging issue is finding the minimum energy point, that occurs in lower voltages due to increased share of the leakage currents.

#### 1.7. RESEARCH OBJECTIVES AND CONTRIBUTIONS

Targeting an ultra low power radio transceiver in 65 nm CMOS technology as mentioned in this chapter and described in more details in chapter 2, this dissertation pursues the following objectives. Likewise, the contributions of this work relies on the presented attempts, suggestions, answers and results obtained out of the underlying research.

• While several low power decoder implementations have been presented [92] [88] [6] [25] [56] [75] [79] [82] [85] [31] [26] [38] [44] [60] [69] [19], especially in recent years, there have been little in-depth investigation based on silicon measurements to evaluate the relative performance and efficiency of alternative analog and digital implementations. While there have been successful designs using both analog and digital circuits, it is not clear which approach is more efficient in the most recent technologies, especially for low rate decoders. Except in the early proof

of concept analog decoding circuits, there has been little side-by-side investigation of analog and digital decoding circuits. Besides, decoding circuits are designed for a wide range of applications, and fabricated using various technologies, which makes it hard to conclusively evaluate the two alternative approaches.

- ECCs and their corresponding decoding algorithms are designed for many diverse applications. The primary focus of the applications could be towards either highest throughput, best error correcting properties, lowest power consumption or least costly in terms of hardware usage. Naturally, there is no ideal solution that satisfies all the mentioned critical factors at the same time. Thus, a trade-off is made such that the primary criteria of interest is satisfied. As an example, wireless medical implants or remote sensor nodes usually do not require high throughput. Instead, low power consumption and minimum hardware usage are the main targets. Considering an ultra low power receiver with predetermined specifications, make it possible to conclude about the most suitable approach.

- While a handful of successfully operating analog decoders have been implemented and reported in the academic literature, so far these circuits have not been able to find their way into real world applications. Therefore, a key question in analog decoding is whether it can be applied to real world applications and what gains can be expected in speed, area and power consumption compared to a digital decoder implementations. The aim of this work is to suggest decoder architectures, either in the analog or digital domain, that can easily be embedded in a low power digital receiver architecture. Therefore, system simulations and performance of digital interface circuitry for analog designs are also included in the investigations.

- Digital circuits operate much slower at reduced supply voltages. In this dissertation, a near-threshold digital decoder design is investigated through measurements to observe the minimum operating voltage, minimum energy point and the related data rates at these operating points.

- Since analog decoding circuits even for the most simple codes can easily include several thousands of transistors, the required Monte-Carlo

12 Introduction

simulation for accurate BER evaluation is not practical. Therefore, simulation of analog decoders has been usually performed through oversimplified methods such as statistical analysis [91]. Such simulations can only offer a rough estimate of the circuit performance at best and perhaps provide some help to modify the critical design factors. Solid evaluation of these circuits is best performed by empirical measures (chip measurements).

• Analog decoding circuits are inherently low power, because sub- $V_T$  operation for CMOS transistors is essentially required. However, performance of analog decoding circuits like other analog circuits are sensitive to non-idealities such as noise, mismatch and process variation which degrades the error correction ability of the circuit. There is a need to investigate how analog decoders perform in recent technologies, as a trade-off between power and BER performance while taking into account a target throughput. Therefore, three versions of analog decoding circuit are fabricated with different transistor sizes to observe how severe the effects of mismatch errors and noise are. Also, what would be the silicon area requirement for a successful operation in comparison with an equivalent digital design?

#### 1.8. OUTLINE OF THE THESIS

This thesis is structured as follows.

#### Part I:

- Chapter 1

- **Chapter 2:** Introduces UPD, a low power radio receiver architecture, as the main target application of this dissertation.

- Chapter 3: Fundamentals and challenges of low power design in the sub-threshold region of a CMOS transistor are discussed in this chapter.

- **Chapter 4:** Introduces the studied coding scheme as well as the corresponding decoding algorithm.

#### Part II:

1.8. Outline of the thesis

Chapter 5: Presents basics of the analog decoding concept as one of the approaches that are followed in this work.

- **Chapter 6:** Provides an overview of the proposed architecture and design aspects of the implemented (7,5) low power analog decoding circuits and reasons behind choosing the critical design factors.

- **Chapter 7:** Summarizes chip measurement results for the implemented (7,5) analog decoders.

#### Part III:

- **Chapter 8:** Introduces an overview of the methods and critical considerations for a low power digital design approach.

- Chapter 9: Provides an overview of the proposed architecture and design aspects of the implemented (7,5) low power equivalent digital decoding circuits and reasons behind choosing the critical design factors.

- Chapter 10: Summarizes chip measurement results for the implemented equivalent (7,5) digital decoder.

#### Part IV:

- **Chapter 11:** Presents an analysis of the results and comparison between the sub-threshold digital and analog design approaches.

- Chapter 12: Provides concluding remarks and introduces potential extensions for future work.

#### Appendices:

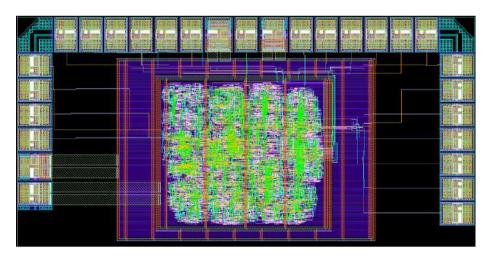

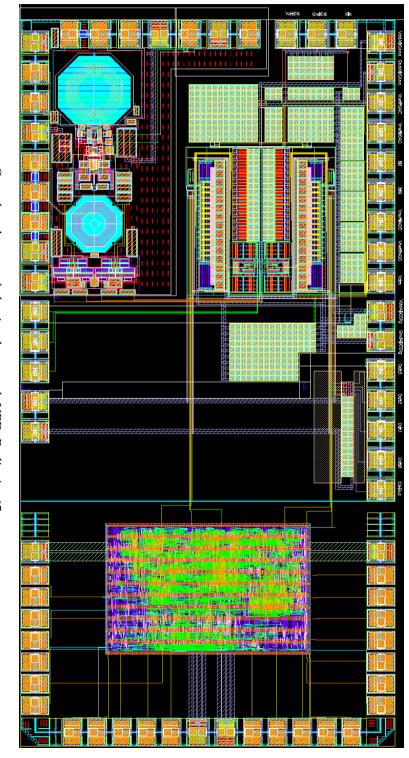

- Appendix A: Layout screenshot of the whole UPD radio receiver chain, as a result of collaboration between multiple researchers, that has been sent for fabrication.

- **Appendix B:** Includes some photos of the measurement setup.

## Ultra Low Power Radio

#### 2.1. INTRODUCTION

Nowadays, wireless connectivity in our everyday life is present more than ever. In addition, there are a range of emerging wireless applications such as Body Area Networks (BAN)s, Wireless Sensor Networks (WSN)s, and a wide diversity of healthcare related devices and medical implants that have attracted dramatic attentions in recent years. These new fields, propose many exciting opportunities and at the same time, present a lot of challenges. Despite the diversity of the applications, these devices or sensors share some common aspects. In addition to being small and highly portable, running on batteries for a long period of time without a need to charge or replace the battery, in some cases for the whole lifetime of the device, is a critical demand. In this regard, one particularly challenging aspect of designing these tiny wireless devices is the implementation of the radio link. The challenge is to provide basic radio connectivity at an extremely low power consumption.

The work presented in this thesis has been carried out as part of a bigger project titled *Wireless Communication for Ultra Portable Devices* or UPD in abbreviation. The UPD project has been funded by *Swedish foundation for strategic research-SSF* and pursues the following goal: A fully integrated and compact short range radio receiver that can be used in ultra low power and portable devices or sensor nodes, such as medical implants, hearing aids, wireless headphones, temperature sensors, etc. Key target specifications of the UPD project are shown in Table 2.1. The operation frequency is chosen within the Industrial, Scientific and Medical (ISM) band which provides 83 MHz of unli-

16 Ultra Low Power Radio

| Total power in active mode | 1 mW              |

|----------------------------|-------------------|

| Total power in standby     | 1 μW              |

| Data rate (uncoded)        | 250 kbps          |

| Data rate (coded)          | 125 kbps          |

| Operating frequency        | 2.45 GHz          |

| Total chip area            | 1 mm <sup>2</sup> |

**Table 2.1.:** UPD project target specifications.

censed bandwidth (2400-2483 MHz).

#### 2.2. THE VISION

Increased popularity of mobile phones directed a lot of research in the past to satisfy the demands for high rate communications. In recent years, however, interests for wireless networks consisting of several low power and low rate communicating nodes have increased. This is due the countless potentials and possibilities that these types of networks introduce. Examples of these networks are WSN and Wireless Body Area Networks (WBAN). WSN can be used for monitoring or sensing the environment and sending the sensed information to other nodes or to a central receiving hub. Similarly, WBAN includes network of devices that are intended to operate inside, on, or around the human body. Each network consists of several nodes or even hundreds; therefore, it is critical for each node to be small and cheap. Operating at ultra low power is easily perceived, since these types of networks are desired to operate for an extended period of time without a need to charge or replace the batteries. The characteristic of communication, in most cases, is transmission at random times, which is when there exists updated data to report. Also, in most applications, each node transmits limited amount of data at each transmission period. Thus, basic transmission at ultra low power and cost is the envisioned device, which introduces design challenges. If the consumed power can be reduced to sufficiently low levels, the required energy can even be harvested from the surrounding environment in forms of heat, motion, etc.

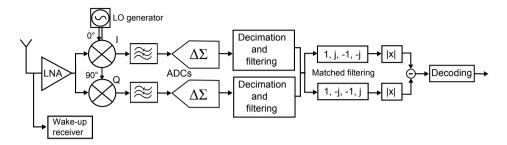

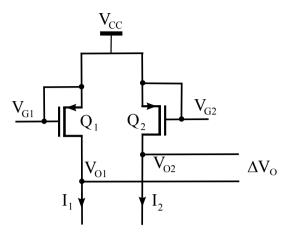

**Figure 2.1.:** UPD receiver architecture.

#### 2.3. THE UPD SYSTEM OVERVIEW

To minimize the size and cost when fabricated in large volumes, the radio transceiver will be realized as a single chip in 65 nanometer CMOS technology. Nanometer CMOS technology is a suitable choice as it offers low cost for implementing digital circuits, and devices with enough speed that allows Radio-Frequency (RF) circuits to operate in weak inversion with extremely low power consumption.

The UPD project has been divided into six research areas: antenna design, RF front-end, analog-to-digital converter, digital baseband, channel decoding and system control <sup>1</sup>.

The aggressive power and area requirements, demand both system level and circuit level design efficiency. The proposed low power UPD receiver architecture is shown in Fig. 2.1. As can be seen, a direct conversion receiver architecture is presented. A direct conversion architecture helps to get rid of the image frequency since the signal after conversion is at low frequency, centered at DC. This helps to simplify the filtering and analog-to-digital conversion circuitry. The accompanied issues of direct conversion, such as presence of DC offsets, are taken care of by the selection of a suitable modulation scheme. The used modulation scheme carries no information at the center of the channel, thus the demodulator becomes insensitive to the DC signals. While different parts of the system have been worked on separately, there has been collaboration between the individuals, to make the receiver operational as a whole. Therefore, the proposed receiver chain, with the accompanying

<sup>&</sup>lt;sup>1</sup>Each sub-project has been carried out by one PhD student. This thesis covers the work which has been done in low power channel decoding.

18 Ultra Low Power Radio

system level simulations carried out as a collaboration between individuals in the UPD project, has been presented in a joint publication (see the preface). To understand the system environment and requirements for operation of the decoder, a summary of different parts of the UPD receiver is presented in the following sub-sections. <sup>2</sup>

#### 2.3.1. ANTENNA DESIGN AND PROPAGATION CHANNEL MEASUREMENTS

Since a significant potential range of applications for an ultra low power radio is on-body communication, medical aids, or bio-implants, the chosen frequency band plays an important role. Apart from the fact that the frequency range 2400-2483 MHz is license-free, operating at this frequency range provides a trade-off between the size of the antenna and the propagation loss around the human body. Operating at lower frequencies, imposes a large size antenna, while there is a limit for the antenna size in the medical applications. On the other hand, the link loss increases at higher frequencies, since tissue absorption of electro-magnetic waves increase. Therefore, small antenna models have been designed and various propagation channel measurements have been performed. Most of the investigations include near-body simulations and measurements, such as the case of ear-to-ear communication (as needed in modern hearing aids). See [17] for more information.

#### 2.3.2. RF FRONT-END

The main function for an RF front-end is to receive high frequency signals from the antenna, amplify the signal in the presence of noise and interference, and convert the radio frequency signals to a much lower frequency range, that is much easier to process. The front-end circuitry includes the Low Noise Amplifier (LNA), mixers, and the associated Local Oscillator (LO). These circuits, since intended to operate at high frequencies, require the highest allocation of power budget. The efficiency and accuracy of these circuits are very important because the signals must have high quality to be useful for the rest of the receiver chain. In addition, the overall sensitivity of the receiver to noise and interference, to a large extent is determined by the performance of the RF

<sup>&</sup>lt;sup>2</sup>Based on the research work on individual blocks, a fully integrated design, from the RF front-end circuitry down to the decoder, has been fabricated in 65 nm CMOS. Measurements are pending at the time of writing of this dissertation.

front-end circuitry. This aspect is even more important in low power receiver designs. In the RF front-end design, to reduce area, inductor-less solutions for the LNA and direct conversion mixers are proposed. Also, an LC oscillator with an on-chip inductor is designed. The quadrature LO signal needed for direct conversion architecture is generated by using a frequency divider, that can be designed with relatively low power consumption. See [11] for more information.

#### 2.3.3. ANALOG TO DIGITAL CONVERTERS

The main requirements for data conversion circuitry are also small area and low power consumption. Still, the dynamic range should be high enough to eliminate the need for any automatic gain control block in the receiver. Thus, to convert the received baseband analog signals to digital domain, continuous time  $\Delta\Sigma$  data converters are used. These types of converters not only provide high resolution at low power consumption, but also have the property of inherent anti-aliasing filtering. The filtering is done by the implemented loop filter in analog domain which relaxes the filtering requirements prior to the Analog-to-Digital Converter (ADC). See [61] for more information.

#### 2.3.4. DIGITAL BASEBAND AND SYNCHRONIZATION

The main functions in digital baseband is digital filtering and demodulation. Data detection and synchronization is also required to locate starting of a data sequence out of the background noise. To design for low power and area, digital filtering is done in a filter chain consisting of four stages of half-band filtering, plus a decimation stage after each filter. The reason for using such a structure is the availability of extremely simple half-band filter structures that require no multiplication. Instead, just a few additions and simple shift operations are needed. Demodulation is performed by the implementation of matched filters on In phase and Quadrature phase (I and Q) received signals. Depending on the received signal, resembling more to the (1,j,-1,-j) sequence or (1,-1,-1,1), the output information bit is decided to be 0 or 1, respectively, in case of uncoded transmission. In the coded mode, the level of resemblance to the mentioned sequences, as defined by the modulation scheme, provides the required soft information for the channel decoder. Four copies of the matched filters with shifted sequences are enough for symbol synchronization. In addition, Barker code preamble and cross-correlation function is devised for data detection. See [72] for more information.

20 Ultra Low Power Radio

#### 2.3.5. CHANNEL DECODER

This sub-project is studied in this dissertation. Use of error correction codes in the system can improve the integrity of data reception by adding algorithmic redundancy to the transmitted data, and then use the added redundancy in the receiver to correct some of the errors. The decoding process is rather complex. Circuits for such purpose, require proper attention in design, to be useful in a small and low power receiver as in the UPD project. Designing a power and area efficient solution that fits the power and area budget of an ultra low power receiver is a challenging task. That is due to the diversity of the error correction codes and the variety of available decoding algorithms, as well as various hardware implementation methods. The proposed solution has to be able to handle the required data rate as well. In the subsequent chapters, the detailed work on this subject is presented.

#### 2.3.6. SYSTEM CONTROL AND WAKE-UP RECEIVER

For a wireless sensor network to operate efficiently, and consume as low power as possible while maintaining the required functionality, devising a Media Access Control (MAC) protocol is essential. A proper MAC protocol not only helps to minimize the power consumption of individual sensor nodes, but also reduces the total power consumption of the network with regard to the target application. In many applications, a continuous transmission of data is not required, rather data is transmitted in infrequent bursts and at random times. Therefore, a wake-up receiver is devised to handle standby and active modes of the sensor nodes. The implemented low power wake-up receiver provides the possibility of significantly reducing the power consumption of the sensor nodes. This is achieved by powering down the nodes when not in use, and activate those again when there is data to be received. Care is taken such that the design of the wake-up receiver and the used protocol, does not lead to unacceptable latency in the wireless network. See [49] for more information.

#### 2.4. UPD MODULATION SCHEME

The choice of modulation plays a critical role in designing a low power radio transmission link, as modulation to a great extent affects the architecture of both transmitter and receiver [20]. One simple option for modulation is On-Off Keying (OOK) [77]. However, this choice can easily lead to out-of-

| RF front-end     | 650 μW |

|------------------|--------|

| ADCs             | 200 μW |

| digital baseband | 120 μW |

| decoding         | 30 μW  |

**Table 2.2.:** UPD initial power budget allocation.

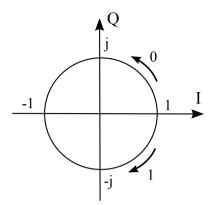

band spurious emissions that disturb other communication. The undesired off-band emissions must be efficiently filtered, which complicates the design of the transmitter. A better choice is constant envelope phase or frequency modulation. In case of UPD, Binary Frequency Shift Keying (BFSK) modulation is considered. Each bit of information is modulated to a sequence of four symbols. Figure 2.2 shows the chosen BFSK modulation on the I/Q plane. The information bits "1"s are encoded to a sequence of 90 degrees clock-wise phase shifts, so that the modulated signal covers a full 360 degree rotation around the I/Q constant amplitude circle. Likewise, the information bits "0"s are encoded by counter-clock-wise rotation. This modulation scheme, significantly simplifies detecting the transmitted information bits in the receiver. Data detection is achieved by multiplying the received complex vectors with a pair of matched filters. One filter is matched to the sequence "1, j, -1, -j", while the other one to "1, -i, -1, j", corresponding to clock-wise and counterclock-wise rotations on the I/Q complex plane. This simple detection has an important advantage, since simplicity in the architecture of the receiver leads to a less power consuming receiver circuitry.

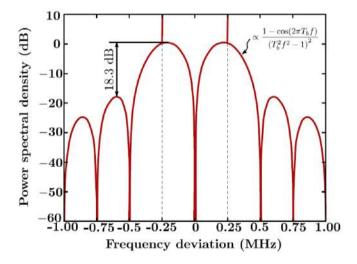

By choosing BFSK with a  $\pm$  250 kHz frequency deviation for 250 kb/s data rate, a notch occurs in the spectrum at the center of the band, as shown in Figure 2.3. Since there is no information transmitted at the center frequency, the demodulation becomes insensitive to the DC offsets and low frequency noise. An FSK modulation, allows demodulation of the signal without detection of the absolute phase, thus, non-coherent demodulation is applied. The sidelobes in the spectrum are considerably weaker than the main lobes (18.3 dB), which can be further suppressed by filtering.

22 Ultra Low Power Radio

**Figure 2.2.:** UPD modulation. The direction of rotation on the I/Q diagram determines the transmitted coded symbol for each information bit.

Figure 2.3.: The ideal BFSK modulation spectrum used in UPD with  $\pm 250\,\mathrm{kHz}$  in-band transmission, corresponding to  $250\,\mathrm{kb/s}$ .

#### 2.5. LOW POWER RADIO STANDARDS

WSN and WBAN are interesting subjects for companies and academia, and currently new standards are being proposed as extensions for IEEE 802.15 series of standards [35]. Among the low power radio standards are Bluetooth Low Energy (BTLE) [9], ZigBee [93], and ANT [3]. BTLE, sometimes marketed as Bluetooth Smart, is currently embedded in some smart phones, and is increasingly used in novel technologies in healthcare, fitness and entertainment industry. Bluetooth Smart, similar to the classic Bluetooth technology, operates in the ISM spectrum range (2.400 GHz-2.4835 GHz), but uses a different set of channels. Within each of the 40, 2 MHz channels in BTLE, data is transmitted using Gaussian Frequency Shift Keying (GFSK) modulation, similar to classic Bluetooth. Over the air data rate is 1 Mbit/s, while the real throughput is 270 kb/s.

The ZigBee protocol is based on IEEE 802.15 standards, and the nodes can operate without a need for a central transceiver or control unit. Data rate defined in ZigBee protocol is 250 kb/s which is suitable for consumer or industrial applications that require short-range wireless transfer of data at low power and relatively low rates. ZigBee can operate at 868 MHz in Europe, 915 MHz in North America and Australia, and 2.4 GHz worldwide. However, data transmission rates vary from 20 kb/s in the 868 MHz frequency band to 250 kb/s in the 2.4 GHz frequency band. For modulation, Binary Phase Shift Keying (BPSK) is used in the 868 and 915 MHz bands, and Offset Quadrature Phase Shift Keying (OQPSK) is applied in the 2.4 GHz band.

Another notable standard to mention is ANT, which is a proprietary open access sensor network protocol, intended to operate in ISM 2.4 GHz band. ANT uses short duty cycle transmissions and deep sleep modes to ensure very low power consumption. In the ANT protocol, nodes can be configured to operate as master or slave and data rate can be up to 1 Mb/s with GFSK modulation.

These general purpose standardized radio solutions generally have 50-100 nJ/b power consumption [10]. For UPD radio communication, the target is to reach much lower levels of power consumption.

#### 2.6. RELEVANCE AND CHALLENGES OF SUB-THRESHOLD DESIGN

For application specific use cases, as are intended for the described low power radio, a non-rechargeable battery is a logical choice. Whereas, the envisioned

24 Ultra Low Power Radio

small size of the transceiver nodes imply limited physical space for batteries. These facts, emphasize the value of the available energy.

One major advantage of a circuit operating in the sub-threshold mode is the ability to generate very low levels of current between the source and drain of the transistors. Analog processing in sub-threshold region is inherently low power since the current levels are low due to weak inversion operation. Low current levels lead to low overall power consumption. Low power decoding in analog domain, uses exponential dependency of drain currents in subthreshold or weak inversion region. Therefore, low power operation not only is achieved, but also is necessary to execute the decoding algorithm. However, due to the exponential relation, parameter variations caused by mismatch and process variations have large effects on the current levels, which in turn tend to reduces the accuracy of processing. Other phenomena such as noise and temperature variations may also degrade performance of analog computing circuitry. How severely these effects will degrade the performance of an analog decoding circuit, is a question that most accurately can be answered by the implementation of prototypes and evaluation via empirical measures; i.e. chip fabrication and measurements.